## Maestro, the Data- and Memory-Aware Middleware for Digital Twin Engines

Utz-Uwe Haus, Christopher Haine, Ali Mohammed, Sebastien Cabaniols

HPE HPC/AI EMEA RESEARCH LAB (ERL)

#### Digital Twins (L1) Descriptive **DIGITAL TWIN** retroactive analysis Computer model (L2) Informative: monitoring & simulation (L3) Predictive: predict evolution of systems (L4) Living: self-adapts to the real system

Digital twins exacerbates the data orchestration problem in HPC

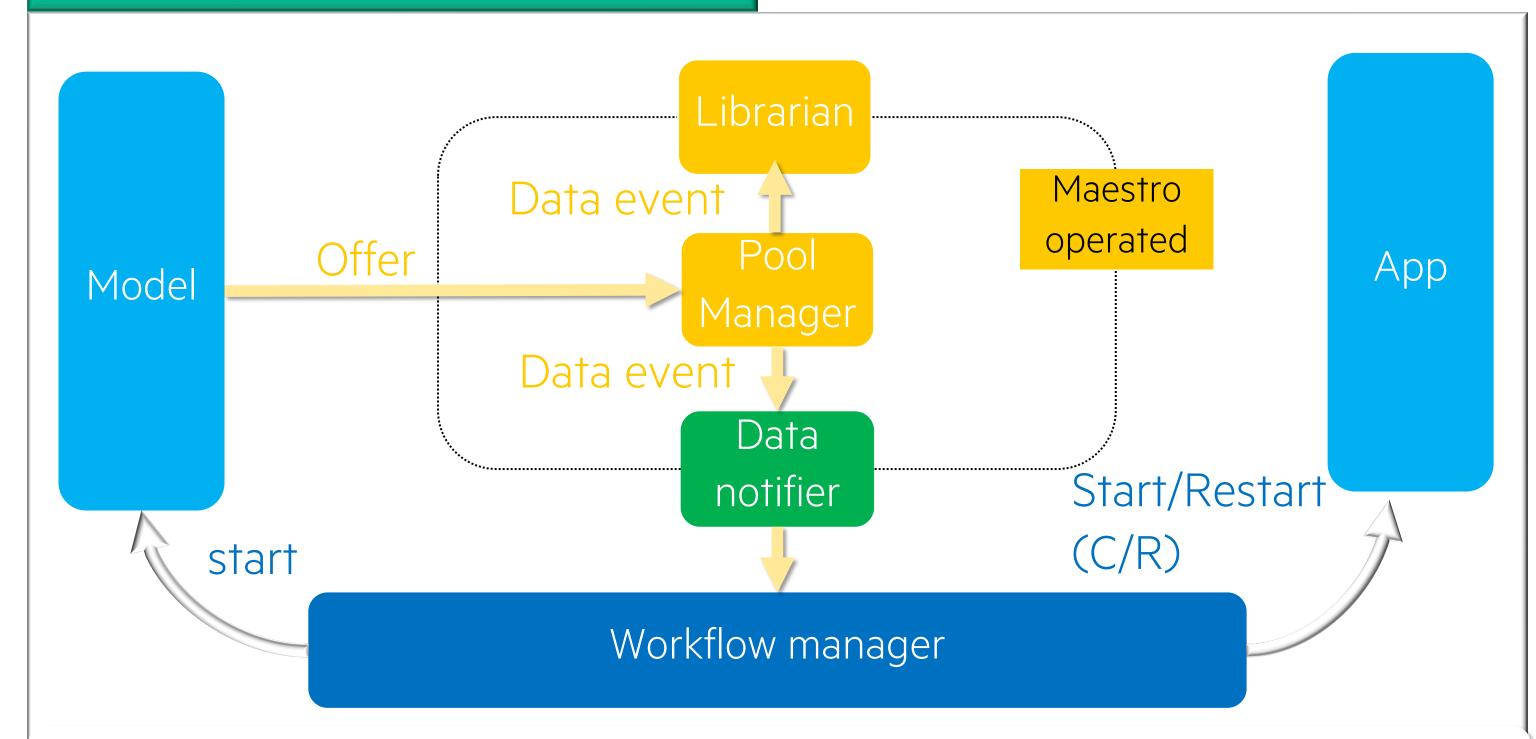

#### Coupling with Workflow

Maestro data events drives the workflow execution

### Climate Adaptation Twin Climate models **NEMO FESOM IFS MultIO** Maestro **AQUA** Data bridge **Impact** model **FDB** App #N Data streaming File read/write **Bypassing filesystem with Maestro**

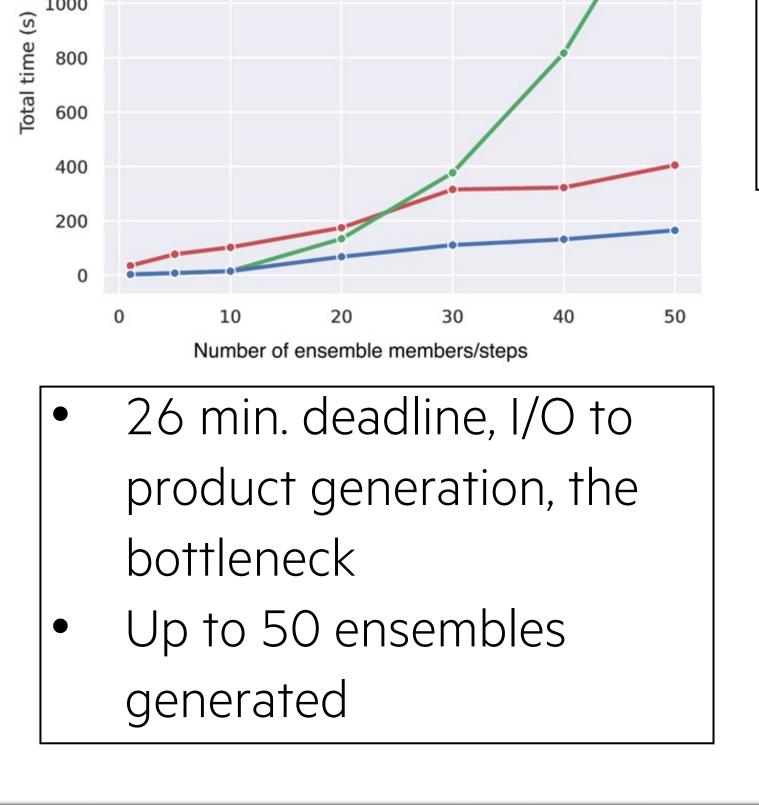

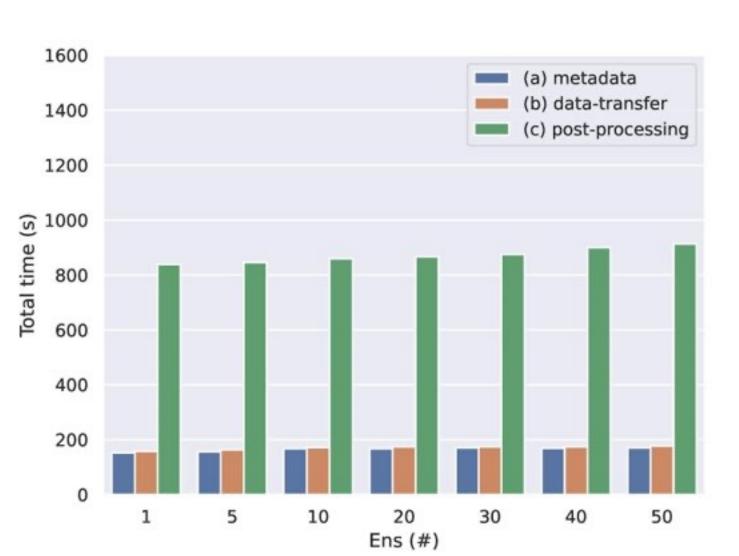

IFS Product Generation Benchmark

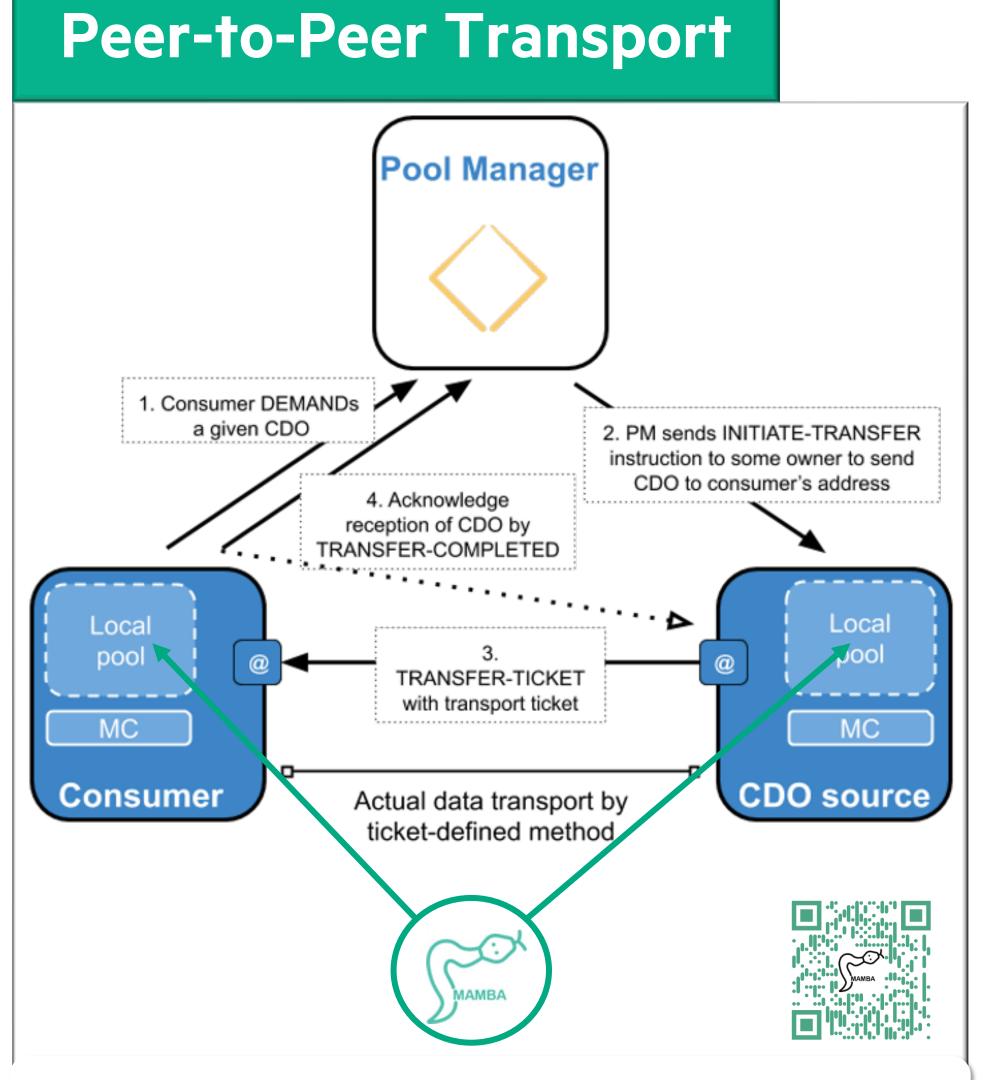

**Direct RDMA between components**

## **Maestro-core Benchmark** .... A: 16 S: 16k .... A: 32 S: 16k

119k CDO-ops/s

1 CXI NIC/Node

thread

Two CQ processing

# Perfect scaling with

- multiple pool managers Up to 2.5 speedup

- compared to FDB

https://www.ecmwf.int/en/about/media-centre/science-blog/2022/secondment-ecmwf-maestro-project

# · A: 16 S: 1k · · · · A: 32 S: 1k 16 32 Number of nodes

- 57k CDO-ops/s

- 1 CXI NIC/Node Single CQ processing thread

- ♦ A: 16 S: 1k

A: 32 S: 1k 120

Number of nodes

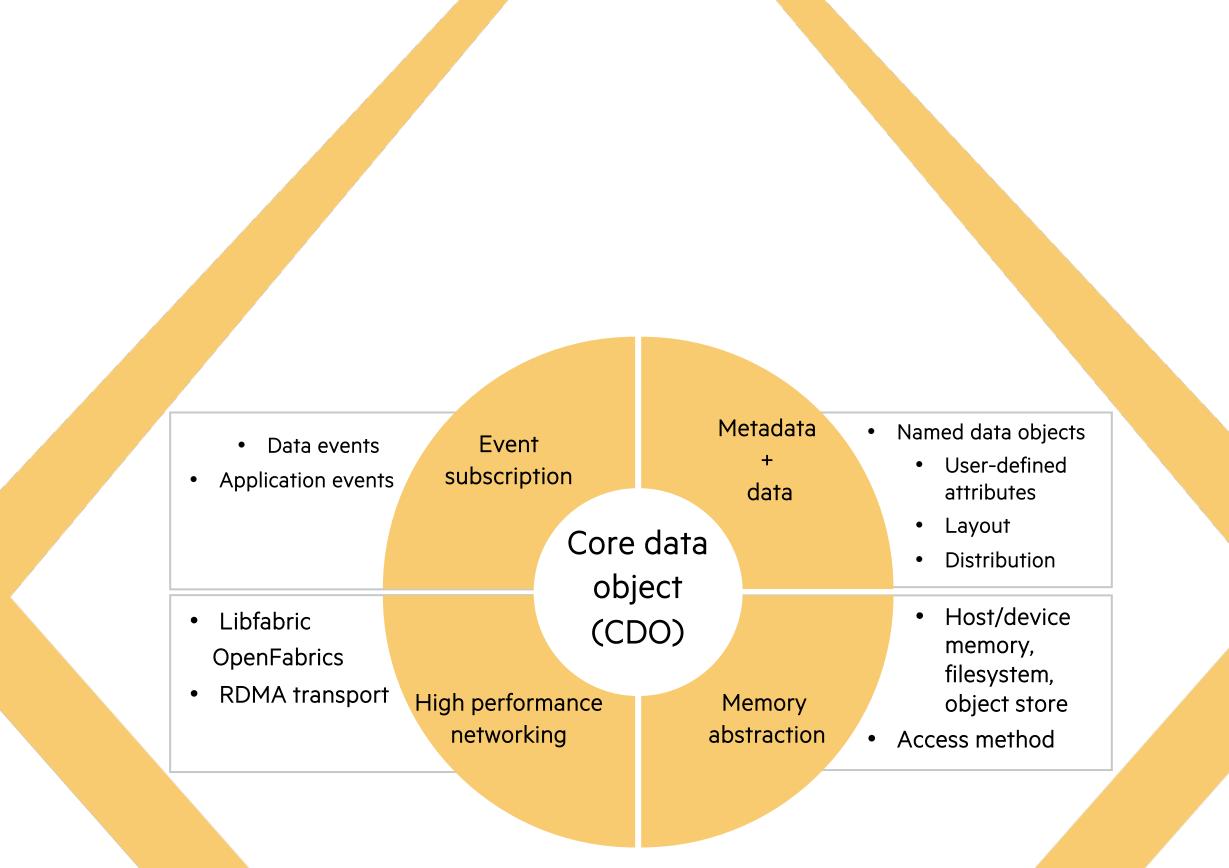

Declaring Maestro CDOs of various number of attributes (A) and attribute sizes (S)